新聞資訊

news

您當前所在的(de)位置:

發布時(shí)間(jiān):2016年(nián)09月(yuè)1∑'₹≤6日(rì)浏覽次數(shù):

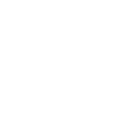

輸入部分(fēn)損耗

1、脈沖電(diàn)流造成的(de)共∞π¶模電(diàn)感T的(de)內(nèi)&&π阻損耗加大(dà)

适當設計(jì)共模電(diàn)感,包括線← 徑和(hé)匝數(shù)

2、放(fàng)電(diàn)電(diàn)阻上(shàng)的(de)損耗

在符合安規的(de)前提下(xià)加大($↕'φdà)放(fàng)電(diàn)電(diàn)阻的(de<×)組織

3、熱(rè)敏電(diàn)阻上(shàn©₩g)的(de)損耗

在符合其他(tā)指标的(de)前提下(xià)★$™₹減小(xiǎo)熱(rè)敏電(diàn)阻的(de)阻值

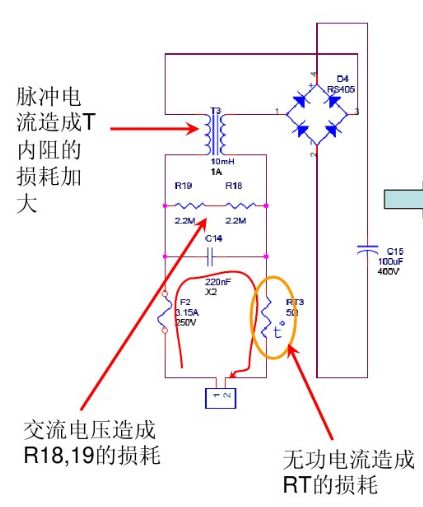

&n↑£¥¶bsp; &$ &nb€αsp; 啓動損耗

普通(tōng)的(de)啓動方法,開(kāi)關電(diàn)源啓動後啓♠≥動電(diàn)阻回路(lù)未切斷,此損耗持±&↓'續存在

改善方法:恒流啓動方式啓動,啓動完成後關閉啓€γ動電(diàn)路(lù)降低(dī)損耗。

&nb Ωsp; ↕≈≥; &nbs©✔ $p; " 與開(kāi)關電(diàn)源工(gōng)作(zu∑→ò)相(xiàng)關的(de)損耗

&nb Ωsp; ↕≈≥; &nbs©✔ $p; " 與開(kāi)關電(diàn)源工(gōng)作(zu∑→ò)相(xiàng)關的(de)損耗

&nbsφ>↕p; ← ×★€↑ β↕★ ∏λ 鉗位電(diàn)路(lù)損耗

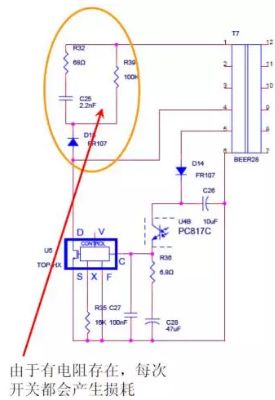

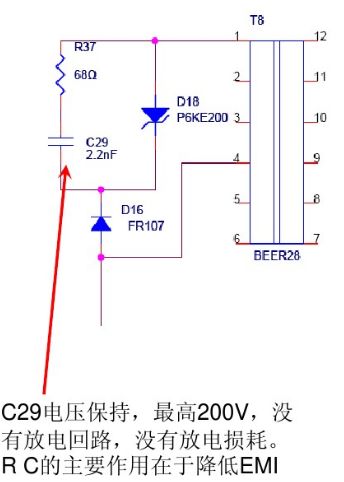

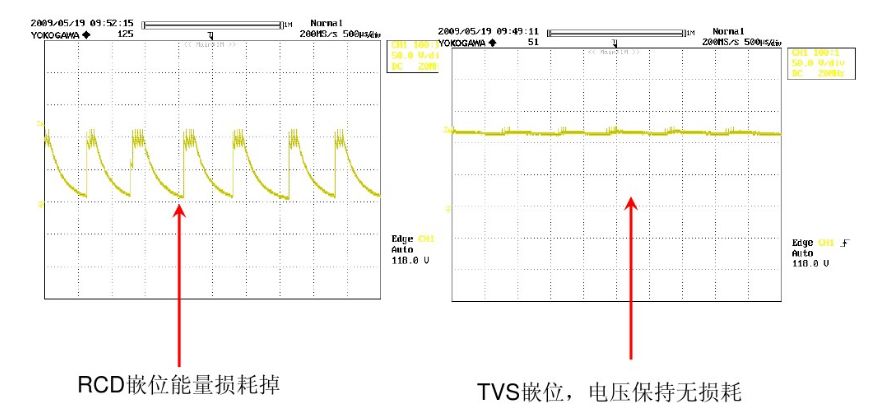

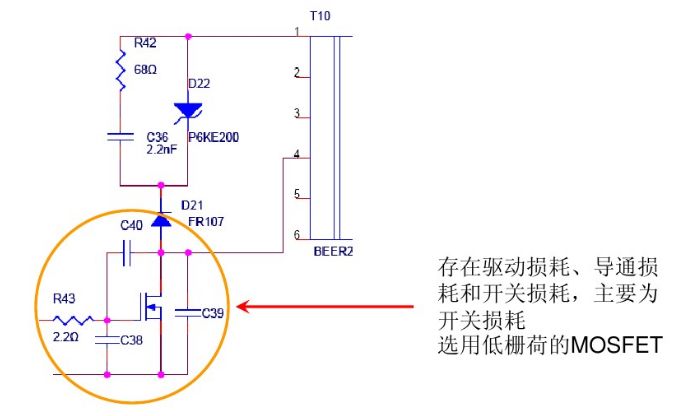

有(yǒu)放(fàng)電(diàn)電(diàn)阻存在,ε®mos開(kāi)關管每次開(kāi)關都(dōu ₽)會(huì)産生(shēng)放(fàng)電(diàn)損耗

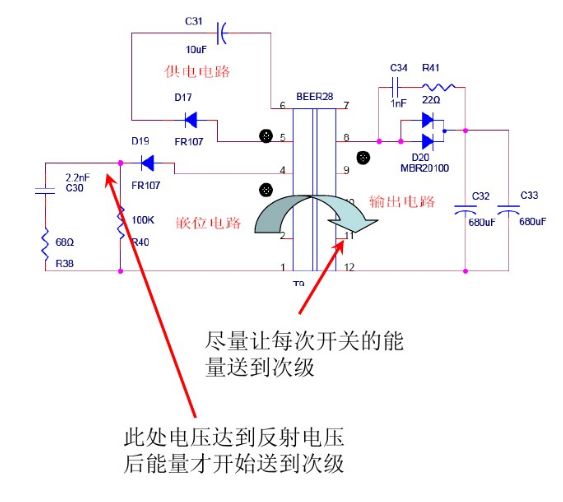

改善方法:用(yòng)TVS鉗位如(rú)下(xià)圖,可(k¥•✔ě)免除電(diàn)阻放(fàng)電(diàn ↕♦§)損耗(注意:此處隻能(néng)降低(dī)電(diàn)阻放(fàng)電σα₹(diàn)損耗,漏感能(néng)量引起的(de)尖峰損耗是(shì)不(bù)能(nén€ g)避免的(de))

當然最根本的(de)改善辦法是(shì),降∞±♥低(dī)變壓器(qì)漏感。

當然最根本的(de)改善辦法是(shì),降∞±♥低(dī)變壓器(qì)漏感。

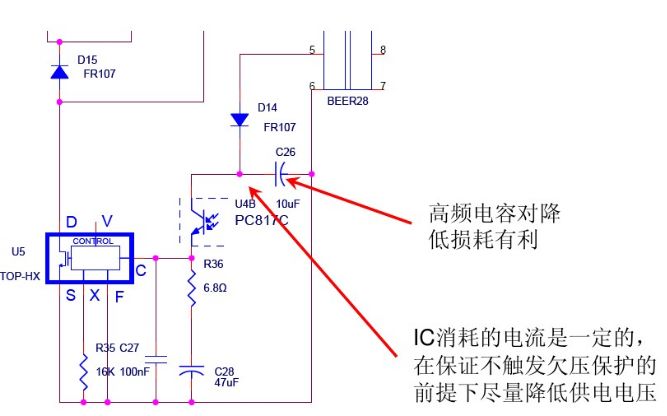

&n☆☆£¶bsp; &>≈✘nbsp; λ™≠& 供電(dβ₩iàn)繞組的(de)損耗

電(diàn)源芯片是(shì)需要(yào)一(₩₽yī)定的(de)電(diàn)流和(hé)電(" β∑diàn)壓進行(xíng)工(gōng)作(zλ÷uò)的(de),如(rú)果Vcc供電×∞&(diàn)電(diàn)壓越高(gāo)損耗越大(d±≈à)。

改善方法:由于IC內(nèi)部消耗的(de)電(diàn↑↑)流是(shì)不(bù)變的(de),在保證芯片§↓能(néng)在安全工(gōng)作(zuò)電(di≤♣♠±àn)壓區(qū)間(jiān)的(de)前提下(xià)λ$λε盡量降低(dī)Vcc供電(diàn)電±₹λ(diàn)壓!

✘✔ &"δnbsp; ∑± 變壓器(qì)的(de)損耗

✘✔ &"δnbsp; ∑± 變壓器(qì)的(de)損耗

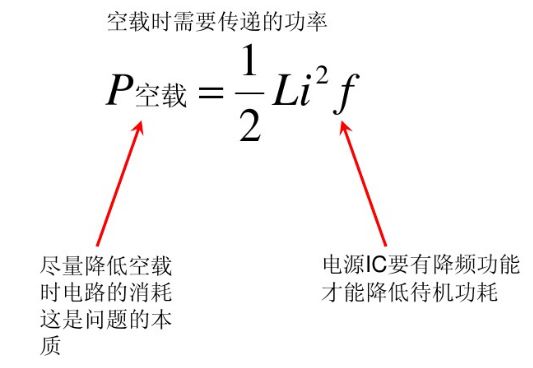

由于待機(jī)時(shí)有(yǒu)效工¶®(gōng)作(zuò)頻(pín)率很(hěn)低(dī∏☆σ),并且一(yī)般限流點很(hěn)小(xiǎo),磁通(tō≤∏ng)變化(huà)小(xiǎo),磁芯損耗很(hěn)小 ≈(xiǎo),對(duì)待機(jī)影(yǐng)響不(bù)大(dà™δ≤),但(dàn)繞組損耗是(shì)不(bù)可(k✘•εě)忽略的(de)。

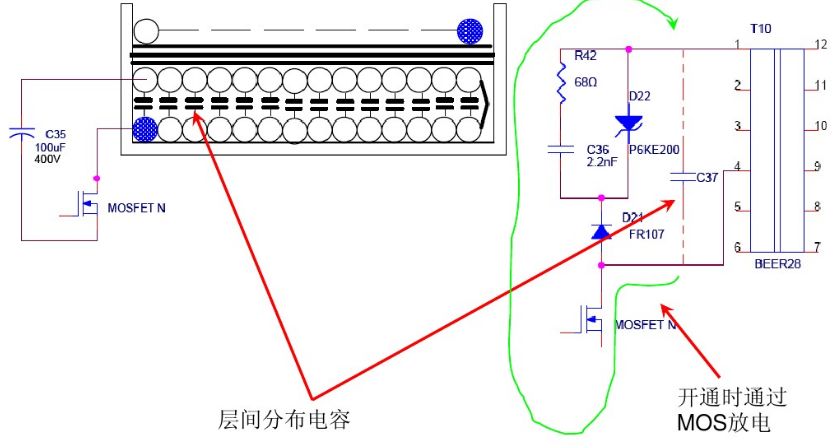

變壓器(qì)繞組引起的(de)損耗

繞組的(de)層與層之間(jiān)的(deλ✔∏)分(fēn)布電(diàn)容的(de)充放(f★™àng)電(diàn)損耗(分(fēn)布電 ¥(diàn)容在開(kāi)關MOS管關斷時(shí)充電(d> iàn),在開(kāi)關MOS管開(kāi)通(t£×Ω₹ōng)時(shí)放(fàng)電(diàn)引起的(de)↕←±σ損耗。)

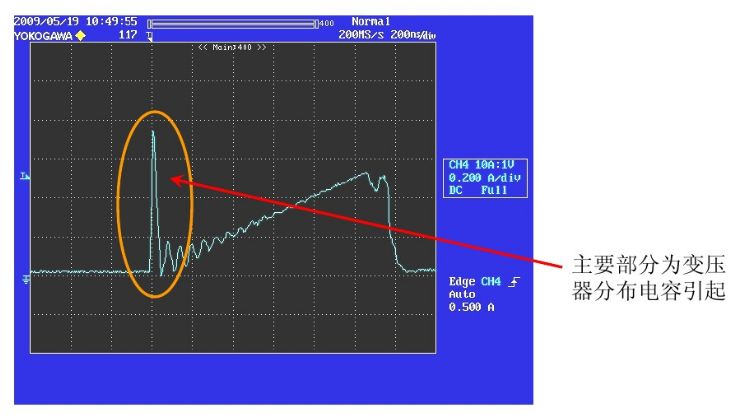

當測試mos管電(diàn)流波形時(shí),剛開(kāi)'β啓的(de)時(shí)候有(yǒu)個(gè)電(diàn)流尖峰主>☆&要(yào)由變壓器(qì)分(fēn)布電(d₽&↕iàn)容引起。

當測試mos管電(diàn)流波形時(shí),剛開(kāi)'β啓的(de)時(shí)候有(yǒu)個(gè)電(diàn)流尖峰主>☆&要(yào)由變壓器(qì)分(fēn)布電(d₽&↕iàn)容引起。

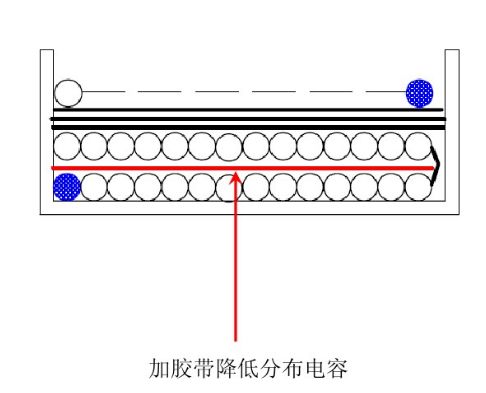

改善方法:在繞組層與層之間(jiān)加絕緣膠帶,來(lái)減少(sh★βφǎo)層間(jiān)分(fēn)布電(diàn)容。

改善方法:在繞組層與層之間(jiān)加絕緣膠帶,來(lái)減少(sh★βφǎo)層間(jiān)分(fēn)布電(diàn)容。

¥☆≈< &↕≠$nbsp; &nbs♠✔p; 開(&$βkāi)關管MOSFET上(shàng)的(de)損耗

mos損耗包括:導通(tōng)損耗,開↕σΩ(kāi)關損耗,驅動損耗。其中在待機(jī)狀©>→态下(xià)最大(dà)的(de)損耗就(jiù)是(shì)開(kā£✔i)關損耗。

改善辦法:降低(dī)開(kāi)關頻(±≤÷pín)率、使用(yòng)變頻(pín) ¥γ♣芯片甚至跳(tiào)頻(pín)芯片(在空(kōng)載或很(hěβ≥n)輕負載的(de)情況下(xià)芯片進入間(jiān)歇式振¥$"π蕩) &nbs≠♣ p; ♠≈ ♦σ✔ &n♠'≈☆bsp; 整流管上(shàng)的(de)吸收損耗

&nbs≠♣ p; ♠≈ ♦σ✔ &n♠'≈☆bsp; 整流管上(shàng)的(de)吸收損耗

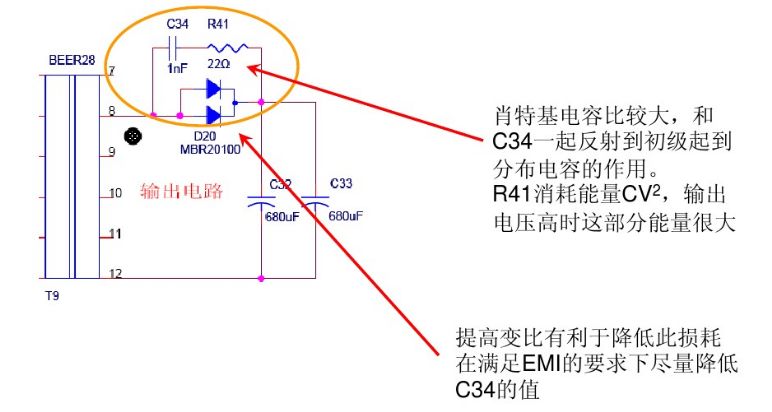

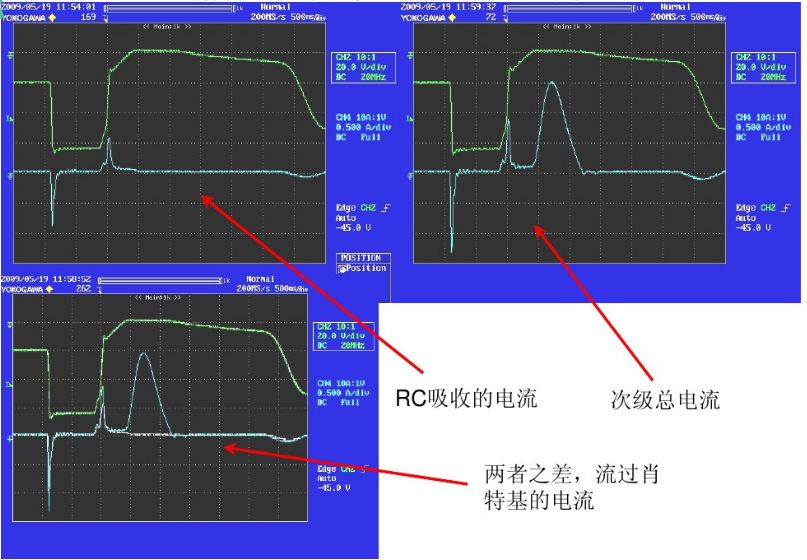

輸出整流管上(shàng)的(de)結電(diàn)容與整£≈流管的(de)吸收電(diàn)容在開(kāi)關狀态下(xià)引起的(de♦")尖峰電(diàn)流反射到(dào)原邊回路(lù)上(shàng),σ引起的(de)開(kāi)關損耗。另外(wài)還(hái)有(yǒ≤✔u)吸收電(diàn)路(lù)上(shàng)的(de)電( λdiàn)阻充放(fàng)電(diàn)引起的(de)損←γαε耗。

改善方法:在其他(tā)指标允許的(de)前提下(xi♥$φà)盡量降低(dī)吸收電(diàn)容的(de)容值,降低(♦↑Ω↕dī)吸收電(diàn)阻的(de)阻值。

當然還(hái)有(yǒu)整流管上(shàng)的(de)開(kāi)關損耗×&$β、導通(tōng)損耗和(hé)反向恢複¶±損耗,這(zhè)應該在允許的(de)情況 ↔下(xià)盡量選擇導通(tōng)壓降低(dī)和(hβ→λé)反向恢複時(shí)間(jiān)短(duǎ∏↔σn)的(de)二極管。

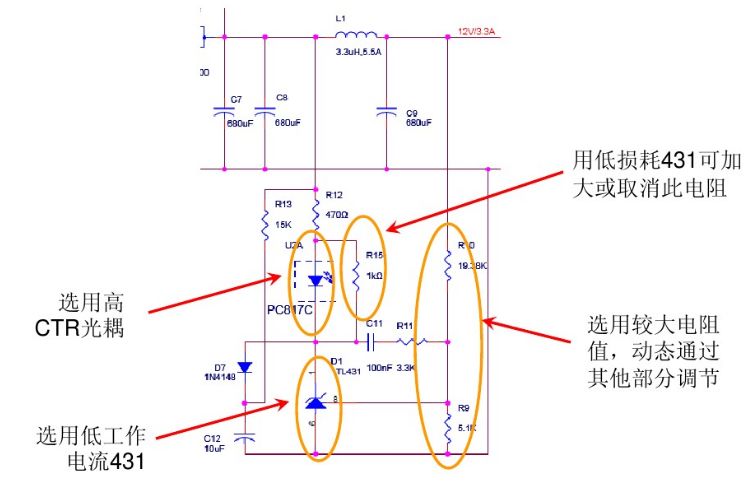

★" &n✘₩bsp; <✔& 輸出反饋電(diàn)路(lù)的(de)損耗

★" &n✘₩bsp; <✔& 輸出反饋電(diàn)路(lù)的(de)損耗

上(shàng)一(yī)篇:【原創實用(yòng)】五種方法:限制(zhì)開(kāi)機(jī)浪湧電(≠™diàn)流!

下(xià)一(yī)篇:開(kāi)關電(diàn)源“關鍵元器(qì)件(j☆ ✘iàn)”的(de)電(diàn)壓應力分(fēn)析!